## 16V/20W High-Integration, High-Efficiency Power Solution for Wireless Power Transmitter

## **FEATURES**

- Input Voltage Range: 4V-16V

- Up to 20W Power Transfer

- Integrated High Efficiency Full-Bridge Power Stage

- Integrated High Efficiency 5V-1ABuck Convertor

- Optimized for EMI

- Build in 3.3V-200mA LDO

- Provide 2.5V Voltage Reference

- Integrated Input Current sense with ±2% accuracy for FOD and modulation

- 3.3V and 5V PWM Signal compatible

- Input Under-Voltage Lockout

- Over current protection

- Thermal shutdown

- 3mm\*4mm QFN-19L Package

- Friendly for PCB layout

## **APPLICATIONS**

- WPC Compliant Wireless Chargers of 7.5W to 15W Systems for Mobiles, Tablets and Wearable devices

- General Wireless Power Transmitters for Consumer, Industrial and Medical Equipment

- Proprietary Wireless Chargers and Transmitters

## DESCRIPTION

The BD7123 is a highly integrated power solution optimized for wireless power transmitter applications. This product can be combined with a specialized controller or general MCU based transmitter controller to achieve high performance, high efficient and cost effective wireless power transmitter system which compliant with WPC specification.

This device integrates all the power functions in a wireless power transmitter including Full bridge power stage, 5V Buck converter, 3.3V LDO and input current sensing to simplify system design and minimize external components thus improve system efficiency.

The integrated Full bridge supports up to 20W power transfer and ensures efficient switching with EMI emission. The build in 5V buck convertor and 3.3V LDO provide power rails to transmitter controller and external equipment and also the power stage driver inside. The build in current detection circuits provides input current information with  $\pm 2\%$  accuracy to support FOD(Foreign Object Detection) and current modulation.

The BD7123 has built-in protection features including input under-voltage lockout, power stage over current protection and short-circuit protection, and thermal shutdown protection.

The BD7123 is available in an 19-pin flip chip QFN 3mm\*4mm package.

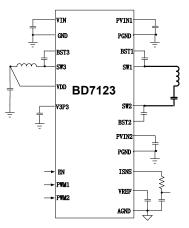

## **TYPICAL APPLICATION**

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature unless otherwise  $\mathsf{noted}^{(1)}$

| DESCRIPTION                                      | MIN  | МАХ | UNIT |

|--------------------------------------------------|------|-----|------|

| VIN                                              | -0.3 | 24  | V    |

| PVIN1, PVIN2                                     | -0.3 | 19  | V    |

| SW1,SW2                                          | -1   | 19  | V    |

| SW3                                              | -1   | 24  | V    |

| BST1,BST2                                        | -0.3 | 25  | V    |

| BST3                                             | -0.3 | 30  | V    |

| BST1-SW1,BST2-SW2,BST3-SW3                       | -0.3 | 6   | V    |

| VDD, V3P3, VREF, ISNS, EN,<br>PWM1, PWM2         | -0.3 | 6   | V    |

| Operating junction temperature TJ <sup>(2)</sup> | -40  | 125 | °C   |

| Storage temperature TSTG                         | -65  | 150 | °C   |

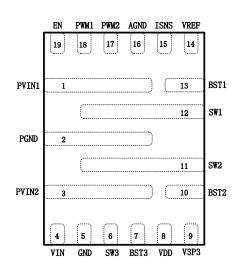

## **PIN CONFIGURATION**

Figure 1. Top view 19-Lead QFN 3mm\*4mm

(1) Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

(2) The IC includes over temperature protection to protect the device during overload conditions. Junction temperature will exceed 150°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

| NAME  | NO. | PIN FUNCTION                                                                                                                                                                                                                                                       |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PVIN1 | 1   | Input supply voltage of half-bridge FETs Q1 and Q2. Connected to the drain of high side FET Q1. a local bypass capacitor from PVIN1 pin to PGND pin should be added. Path from PVIN1 pin to high frequency bypass capacitor and PGND must be as short as possible. |

| PGND  | 2   | PGND is the common power ground of full bridge, connected to the source terminal of low side FETs Q2 and Q4 internally.                                                                                                                                            |

| PVIN2 | 3   | Input supply voltage of half-bridge FETs Q3 and Q4. Connected to the drain of high side FET Q1. Local bypass capacitor from PVIN1 pin to PGND pin should be added. Path from PVIN1 pin to high frequency bypass capacitor and PGND must be as short as possible.   |

| VIN   | 4   | Input supply voltage of buck convertor. A local bypass capacitor from VIN pin to GND pin should be added. Path from VIN pin to high frequency bypass capacitor and GND must be as short as possible.                                                               |

| GND   | 5   | Power ground of buck convertor.                                                                                                                                                                                                                                    |

| SW3   | 6   | Regulator switching output. Connect SW3 to an external power inductor.                                                                                                                                                                                             |

| BST3  | 7   | Power supply bias for the high-side power MOSFET gate driver of buck convertor. Connect a 0.1uF capacitor from BST3 pin to SW3 pin.                                                                                                                                |

# **PIN FUNCTIONS**

| VDD  | 8  | Buck convertor 5V output voltage, connect 22uF capacitor from this pin to GND. VDD is also the power supply for gate driver of power stage and as the input power for 3.3V LDO.                                                                                                                    |

|------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V3P3 | 9  | 3.3V LDO output. Connect 1uF capacitor to ground.                                                                                                                                                                                                                                                  |

| BST2 | 10 | Power supply bias for the high-side power MOSFET gate driver of Q3 as shown in the block diagram. Connect a 0.1uF capacitor from BST2 pin to SW2 pin.                                                                                                                                              |

| SW2  | 11 | Switching node of the half-bridge FETs Q3 and Q4, as shown in the block diagram.                                                                                                                                                                                                                   |

| SW1  | 12 | Switching node of the half-bridge FETs Q1 and Q2, as shown in the block diagram.                                                                                                                                                                                                                   |

| BST1 | 13 | Power supply bias for the high-side power MOSFET gate driver of Q1 as shown in the block diagram. Connect a 0.1uF capacitor from BST1 pin to SW1 pin.                                                                                                                                              |

| VREF | 14 | Output of the 2.5V LDO. connect 1uF capacitor to ground.                                                                                                                                                                                                                                           |

| ISNS | 15 | Current detection output. The voltage of the pin is proportional to the input current.                                                                                                                                                                                                             |

| AGND | 16 | Analog ground of the IC                                                                                                                                                                                                                                                                            |

| PWM2 | 17 | PWM logic input to the FET Q3 and Q4 as shown in the Block Diagram. Logic HIGH turns off the low-side FET Q4, and turns on the high-side FET Q3. Logic LOW turns off the high-side FET Q3 and turns on the low-side FET Q4. When PWM input is in the tristate mode, both Q3 and Q4 are turned off. |

| PWM1 | 18 | PWM logic input to the FET Q1 and Q2 as shown in the Block Diagram. Logic HIGH turns off the low-side FET Q2, and turns on the high-side FET Q1. Logic LOW turns off the high-side FET Q1 and turns on the low-side FET Q2. When PWM input is in the tristate mode, both Q1 and Q2 are turned off. |

| EN   | 19 | Chip enable pin. Pull the pin high or keep it floating to enable the IC. When chip enable, Buck convertor will start to work if VIN higher than UVLO threshold. After VDD is established, power stage can respond to PWM input logic then.                                                         |

## **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range unless otherwise noted

| PARAMETER       | DEFINITION                     | MIN | МАХ | UNIT |

|-----------------|--------------------------------|-----|-----|------|

| V <sub>IN</sub> | Input voltage range            | 4   | 20  | V    |

| TJ              | Operating junction temperature | -40 | 150 | °C   |

## **ESD RATINGS**

| PARAMETER        | DEFINITION                                                                                  | MIN  | МАХ  | UNIT |

|------------------|---------------------------------------------------------------------------------------------|------|------|------|

| M                | Human Body Model(HBM), per ANSI-JEDEC-JS-001-2014 specification, all pins <sup>(1)</sup>    | -2   | +2   | kV   |

| V <sub>ESD</sub> | Charged Device Model(CDM), per ANSI-JEDEC-JS-002-2014specification, all pins <sup>(2)</sup> | -0.5 | +0.5 | kV   |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## **THERMAL INFORMATION**

| PARAMETER             | THERMAL METRIC                                        | DFN-19L | UNIT |

|-----------------------|-------------------------------------------------------|---------|------|

| R <sub>θJA</sub>      | Junction to ambient thermal resistance <sup>(1)</sup> | 42      | °C/W |

| $R_{	extsf{	heta}JC}$ | Junction to case thermal resistance <sup>(1)</sup>    | 45      | C/vv |

(1) SCT provides  $R_{\theta JA}$  and  $R_{\theta JC}$  numbers only as reference to estimate junction temperatures of the devices.  $R_{\theta JA}$  and  $R_{\theta JC}$  are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT63240 is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink

that is soldered to the leads of the BD7123. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual  $R_{\text{BJA}}$  and  $R_{\text{BJC}}$ .

## **ELECTRICAL CHARACTERISTICS**

V<sub>IN</sub>=V<sub>PVIN1</sub>=V<sub>PIN2</sub>=12V, VDD=5V, T<sub>J</sub>=-40°C~85°C, typical value is tested under 25°C.

| SYMBOL PARAMETER | TEST CONDITION | MIN | ТҮР | MAX | UNIT |

|------------------|----------------|-----|-----|-----|------|

|------------------|----------------|-----|-----|-----|------|

### Input supplies and UVLO

| V <sub>IN</sub>        | Operating input voltage             |                                                                       | 4   | 16 | V  |

|------------------------|-------------------------------------|-----------------------------------------------------------------------|-----|----|----|

| Vin uvlo               | Input UVLO Threshold                | V <sub>IN</sub> rising                                                | 3.6 | ;  | V  |

| VIN_UVLO               | Hysteresis                          |                                                                       | 400 | )  | mV |

| I <sub>SHDN</sub>      | Shutdown current from VIN pin       | EN=0V, VIN=12V                                                        | 1   | 2  | μA |

| I <sub>SHDN_PVIN</sub> | Shutdown current from PVIN1,PVIN2   | EN=0V, PVIN=12V                                                       | 1   | 2  | uA |

| I <sub>SHDN_VDD</sub>  | Shutdown current from VDD           | EN=0V, VDD=5V                                                         | 1   | 2  | uA |

| I <sub>VINQ</sub>      | Quiescent current from VIN pin      | EN floating, VDD=5.5V, no<br>switching, no loading on Buck<br>and LDO | 120 | )  | uA |

| I <sub>PVINQ</sub>     | Quiescent current from PVIN1, PVIN2 | EN floating, VDD=5.5V, no<br>switching, no loading on Buck<br>and LDO | 50  |    | uA |

| lq                     | Quiescent current from VDD pin      | EN floating, VDD=5.5V, no<br>switching, no loading on Buck<br>and LDO | 200 | )  | uA |

#### **ENABLE INPUTS and PWM logic**

| $V_{\text{EN}_{\text{H}}}$ | Enable high threshold        |                   |      | 1.18 |      | V  |

|----------------------------|------------------------------|-------------------|------|------|------|----|

| $V_{\text{EN}_{\text{L}}}$ | Enable low threshold         |                   |      | 1.1  |      | V  |

| V <sub>IH</sub>            | PWM1, PWM2 Logic level high  | V3P3=3.3V, VDD=5V | 2.65 |      |      | V  |

| VIL                        | PWM1, PWM2 Logic level low   | V3P3=3.3V, VDD=5V |      |      | 0.55 | V  |

| V <sub>TS</sub>            | PWM1, PWM2 Tri-state voltage |                   | 1.2  |      | 2    | V  |

| T <sub>THOLD</sub>         | Tri-state activation time    |                   |      | 60   |      | ns |

#### **Buck convertor**

| F <sub>SW</sub>     | Switching frequency                                    |      | 600 |      | KHz |

|---------------------|--------------------------------------------------------|------|-----|------|-----|

| V <sub>DD</sub>     | Output voltage                                         | 4.95 | 5   | 5.05 | V   |

| I <sub>LIM_HS</sub> | High-side power MOSFET peak<br>current limit threshold |      | 1.5 |      | А   |

| tss                 | Internal soft-start time                               |      | 1   |      | ms  |

#### 3.3V LDO

| V <sub>3P3</sub> | Output voltage            | Cout=1uF, VDD=5V, T <sub>A</sub> =25℃ | 3.2 | 3.3 | 3.4 | V  |

|------------------|---------------------------|---------------------------------------|-----|-----|-----|----|

| I <sub>3P3</sub> | Output current Capability |                                       | 200 |     |     | mA |

| I <sub>SC</sub>  | Short current             |                                       |     | 50  |     | mA |

#### 2.5V REFFERENCE OUTPUT

| $V_{2P5}$        | Output voltage reference  | 2.45 | 2.5 | 2.55 | V  |

|------------------|---------------------------|------|-----|------|----|

| I <sub>3P3</sub> | Output current Capability | 100  |     |      | mA |

| I <sub>SC</sub>  | Short current             |      | 50  |      | mA |

#### **Current Sense**

| VISNS0             | Voltage with no input current | I <sub>PVIN</sub> =0A ,Tj=25℃ | 0.6 | V |

|--------------------|-------------------------------|-------------------------------|-----|---|

| V <sub>ISNS1</sub> | Voltage with 1A input current | I <sub>PVIN</sub> =1A, Tj=25℃ | 1.2 | V |

| SYMBOL             | PARAMETER                            | TEST CONDITION                  | MIN | ΤΥΡ | MAX | UNIT |

|--------------------|--------------------------------------|---------------------------------|-----|-----|-----|------|

| V <sub>ISNS2</sub> | Voltage with 1.6A input current      | I <sub>PVIN</sub> =1.6A, Tj=25℃ |     | 2.2 |     | V    |

| RISNS              | Input current to output voltage gain | VISNS=VISNS0+IPVIN*RISNS        |     | 1   |     | V/A  |

| Protection         |                                      |                                 |     |     |     |      |

| T <sub>SD</sub>    | Thermal shutdown threshold           | T <sub>J</sub> rising           |     | 155 |     | °C   |

|                    | Hysteresis                           |                                 |     | 35  |     | °C   |

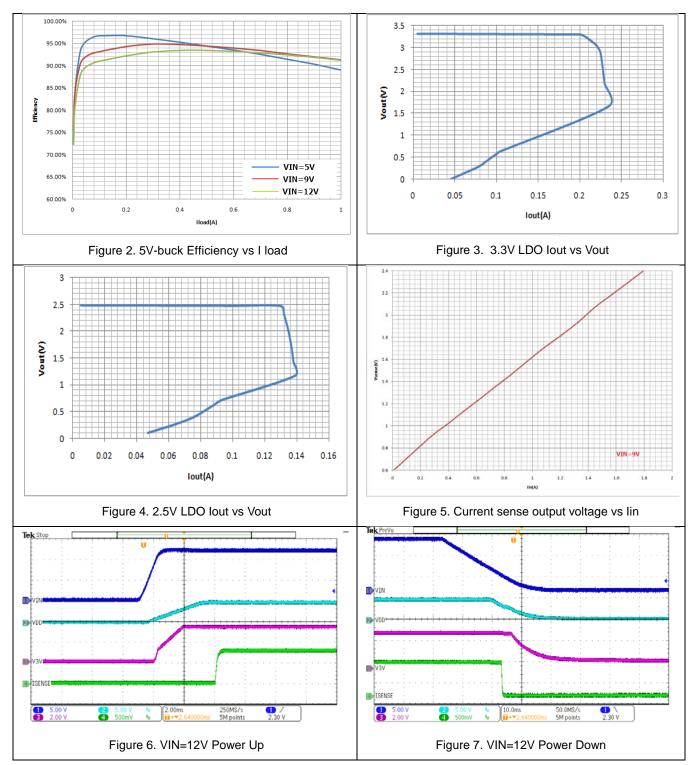

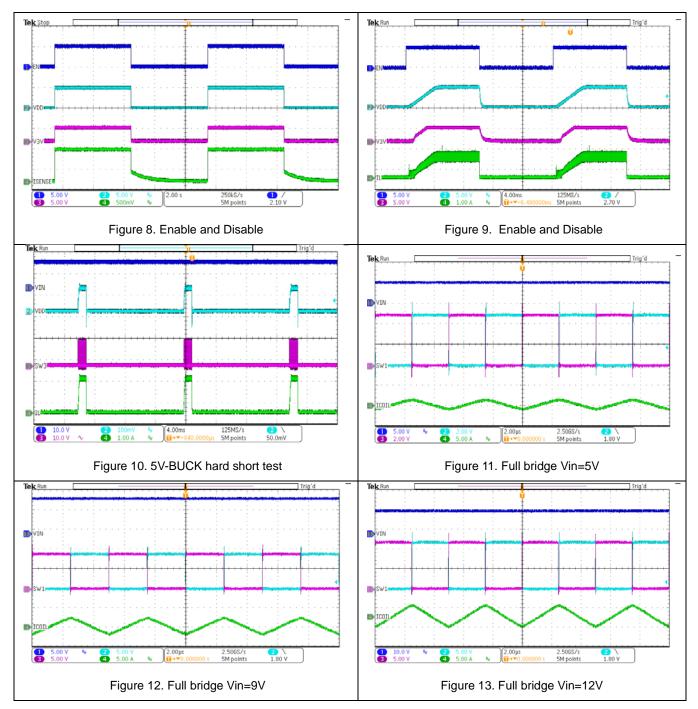

## **TYPICAL TEST RESULTS**

# **TYPICAL TEST RESULTS**

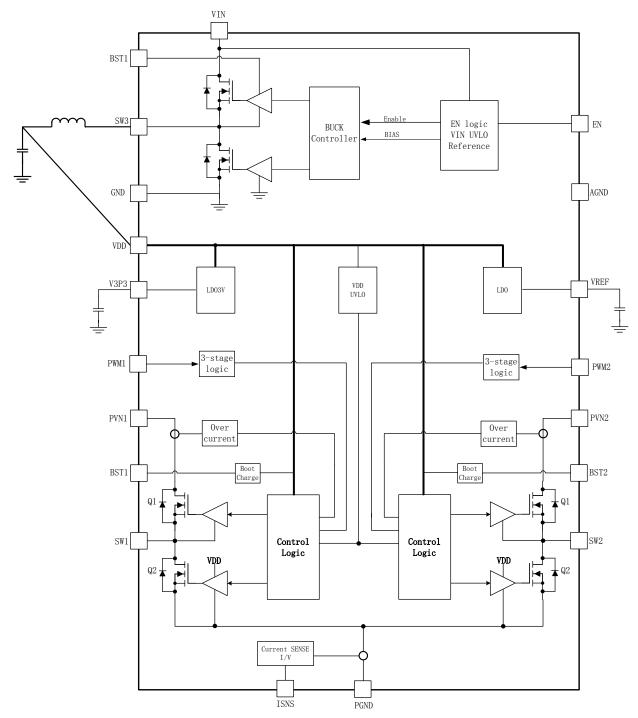

## FUNCTIONAL BLOCK DIAGRAM

Figure 14. Functional Block Diagram

# **APPLICATION INFORMATION**

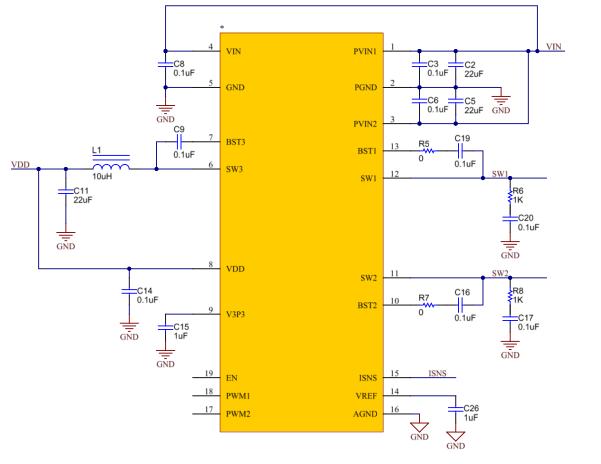

### **Typical Application**

GND

GND

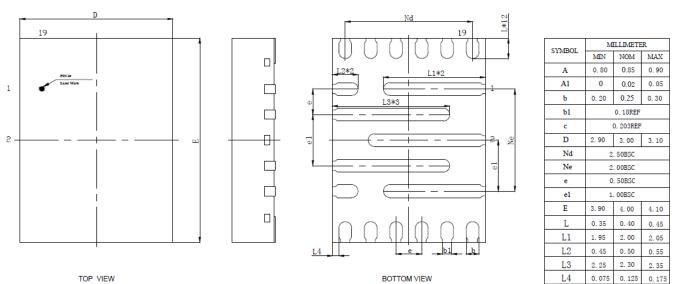

## **PACKAGE INFORMATION**

### 特别申明:

本资料内容如有更改,恕不另行通知。

深圳市蜜蜂电子有限公司是不负责造成的本文所述电路或图表的任何问题,其相关的工业产权,专利或其他权利属 于第三方。另外,应用电路示例解释产品的典型应用,并不能保证任何具体的大规模生产设计的成功。

严禁利用本文所述用于其他目的和/或无深圳市蜜蜂电子有限公司的明确许可,转载或复制的信息。

本文描述的产品不能使用任何装置说出者实放在之主服心,可如健身器材,医疗器械,安全系统,燃气设备,或安装

在飞机和其他车辆的任何设备,无需深圳市蜜蜂电子有限公司的事先书面许可。 5.虽然深圳市蜜蜂电子有限公司发挥最大可能的努力,以确保高品质和可靠性,半导体产品的故障或故障可能发生。 因此,这些产品的用户应该对安全性的设计给予充分考虑,包括冗余,防火措施和故障预防,防止任何意外,火灾,

社会性损害可能发生。

### Important Statement:

1. The information described herein is subject to change without notice.

2.ShenZhen Bee Electronics Co., Ltd. is not responsible for any problems caused by circuits or

diagrams described herein whose related industrial properties, patents, or other rights belong to third parties. The a pplication circuit examples explain typical applications of the products, and do not guarantee the success of any specific mass-production design.

3. Use of the information described herein for other purposes and/or reproduction or copying without the express permission of ShenZhen Bee Electronics Co., Ltd. is strictly prohibited.

4. The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of ShenZhen Bee Electronics Co., Ltd.

5.Although ShenZhen Bee Electronics Co., Ltd. exerts the greatest possible effort to ensure high quality and reliability, the failure or malfunction of semiconductor products may occur. The user of these products should therefore give thorough consideration to safety design, including redundancy, fire-prevention measures, and malfunction prevention, to prevent any accidents, fires, or community damage that may ensue.